こんにちは、whatacottonです。今日も今日とてパソコンをしているのですが、先日技術書典で東京に行くついでに秋葉原に寄ることにしました!

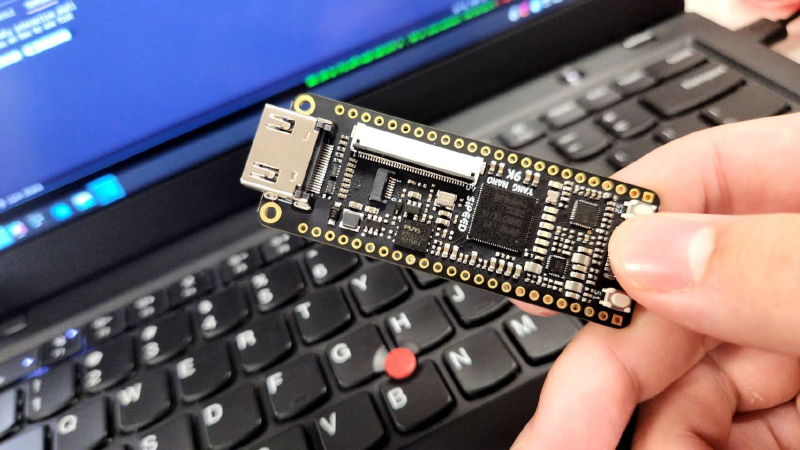

最近verilogを書いていたので実際に回路を焼いて動かしてみたいという強い気持ちがあり、もともと目星をつけていたのですが、ついに秋月で購入してきました!

Tang Nano 9kを!!

本記事はこの記事を参考にしています。

#

Tand Nano 9kとは

Tang Nano 9kとは中国のSipeedが出している、Gowin GW1NR-9 FPGAチップをベースにした安価なFPGAボードです。

FPGAボードとは自分で論理回路を実装し、焼くことでそのとおりに動かしたりできる特殊なICチップが乗っている基盤のことです。

Tang Nano 9kに関する詳しい情報は以下のリンクを確認してください。

Tang Nano 9K - Sipeed Wiki

#

まずはIDEをインストールした

回路を焼き付けるためにはそのためのアプリケーションが必要で、この方のように直接コマンドを駆使して焼く方法もあるらしいのですが、今回はIDEを選択しました。

IDEダウンロード公式サイト

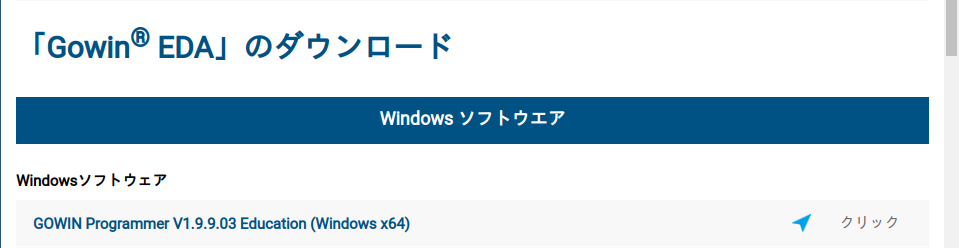

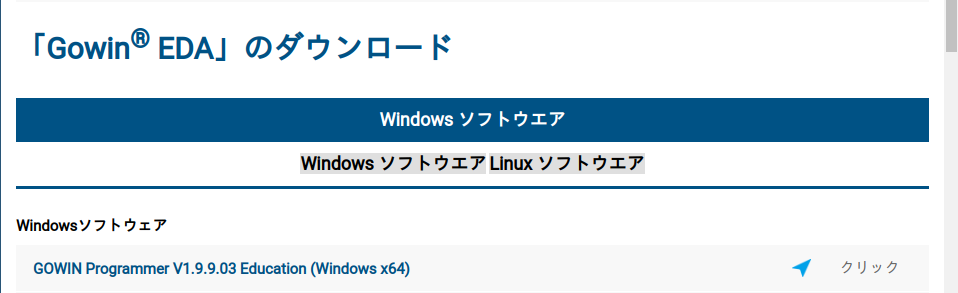

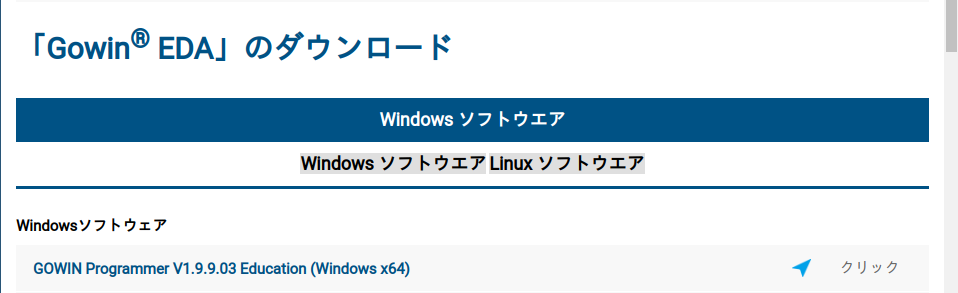

IDEのインストールサイトでレスポンシブ対応によってlinux向けのパッケージが隠れてしまうので注意してください。クリックすると一応選択肢が出てきます。(1敗)

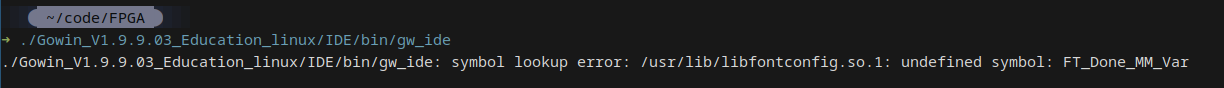

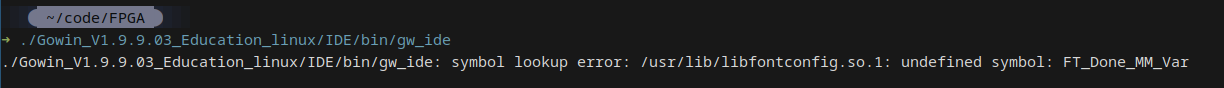

パッケージをダウンロードして解凍したら、そのまま実行できます。と言いたかったのですが、エラーを踏んでしまいました。

どうやら

1

|

$ export 'LD_PRELOAD=/usr/lib64/libfreetype.so'

|

これを実行してから実行すると良いらしいです。

#

問題発生

参考の記事通り進んでいたのですが、またエラーを踏んでしまいました。 USBを読んでくれませんでした… というかprogrammerが実行できませんでした…

Gowin EDA のダウンロードとインストール2(Gowin Programmer のドライバをインストール)-FPGAの部屋

この記事によると、USBのドライバを別で起動する必要がありそう。

ということで、IDEのダウンロードページの下の方にあるGowin programmerをダウンロードして解凍し、

1

|

$ sudo ./Programmer/bin/Gowin_USB_Cable_Installer.sh

|

実行しました。このとき管理者権限で実行する必要があります。これでIDE側でprogrammerが起動してくれればいいのですが、起動しない場合は

1

|

$ sudo ./Programmer/bin/programmer

|

を実行し、直接起動しましょう。

これでprogrammerというアプリケーションが起動し、FPGAに焼くことができる様になりました。

#

終わりに

とりあえず少し触っただけなのですが、とても楽しかったです!これからもっと色々なことをしてみたいと思います!

#

補遺

きれいなコードとは言えないかもしれませんが、ボタンを押したら順番にLEDが光るプログラムをおいておきます。2つのボタンを同時に押すことでLEDの位置をリセットできます。

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

|

`default_nettype none

module top (

input wire IN_A,

input wire RST,

input wire CLK,

output wire OUT_A,

output wire OUT_B,

output wire OUT_C,

output wire OUT_D,

output wire OUT_E,

output wire OUT_F

);

reg [5:0] r_state;

assign OUT_A = ~r_state[0];

assign OUT_B = ~r_state[1];

assign OUT_C = ~r_state[2];

assign OUT_D = ~r_state[3];

assign OUT_E = ~r_state[4];

assign OUT_F = ~r_state[5];

always @(posedge IN_A)begin

if(~RST)begin

r_state <= 6'b000001;

end else begin

if(r_state[0])begin

r_state <= 6'b000010;

end else if(r_state[1])begin

r_state <= 6'b000100;

end else if(r_state[2])begin

r_state <= 6'b001000;

end else if(r_state[3])begin

r_state <= 6'b010000;

end else if(r_state[4])begin

r_state <= 6'b100000;

end else if(r_state[5])begin

r_state <= 6'b000001;

end

end

end

endmodule

`default_nettype wire

|

cstファイル

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

|

//Copyright (C)2014-2024 Gowin Semiconductor Corporation.

//All rights reserved.

//File Title: Physical Constraints file

//Tool Version: V1.9.9.03 Education

//Part Number: GW1NR-LV9QN88PC6/I5

//Device: GW1NR-9

//Device Version: C

//Created Time: Mon 05 27 18:25:42 2024

IO_LOC "OUT_F" 16;

IO_PORT "OUT_F" IO_TYPE=LVCMOS18 PULL_MODE=UP DRIVE=8 BANK_VCCIO=1.8;

IO_LOC "OUT_E" 15;

IO_PORT "OUT_E" IO_TYPE=LVCMOS18 PULL_MODE=UP DRIVE=8 BANK_VCCIO=1.8;

IO_LOC "OUT_D" 14;

IO_PORT "OUT_D" IO_TYPE=LVCMOS18 PULL_MODE=UP DRIVE=8 BANK_VCCIO=1.8;

IO_LOC "OUT_C" 13;

IO_PORT "OUT_C" IO_TYPE=LVCMOS18 PULL_MODE=UP DRIVE=8 BANK_VCCIO=1.8;

IO_LOC "OUT_B" 11;

IO_PORT "OUT_B" IO_TYPE=LVCMOS18 PULL_MODE=UP DRIVE=8 BANK_VCCIO=1.8;

IO_LOC "OUT_A" 10;

IO_PORT "OUT_A" IO_TYPE=LVCMOS18 PULL_MODE=UP DRIVE=8 BANK_VCCIO=1.8;

IO_LOC "RST" 4;

IO_PORT "RST" IO_TYPE=LVCMOS18 PULL_MODE=UP BANK_VCCIO=1.8;

IO_LOC "IN_A" 3;

IO_PORT "IN_A" IO_TYPE=LVCMOS18 PULL_MODE=UP BANK_VCCIO=1.8;

IO_LOC "CLK" 52;

IO_PORT "CLK" IO_TYPE=LVCMOS18 PULL_MODE=UP BANK_VCCIO=1.8;

|

LEDやボタンがアクティブ-Lになっているのですが、これはプルアップ回路になっていることが原因だそうです。(知り合いに教えていただきました。)